Đối với hàm NOT khi đầu vào là A thì ta thu được kết quả:

Trong các phát biểu dưới đây phát biểu nào sai?

A. Tất cả đều đúng

B. Với dạng chuẩn tắc tuyển đầy đủ dùng dấu “∑” để lập tổng của các tổ hợp biến mà hàm có giá trị bằng 1

C. Dạng chuẩn tắc tuyển đầy đủ là tổn của nhiều thành phần, mà mỗi thành phần là một tích đầy đủ của n biến

D. Dạng chuẩn tắc tuyển đầy đủ còn được gọi là tổng các tích

Trong các quy tắc dưới đây quy tắc nào sai:

Hãy chỉ ra phát biểu đúng trong các phát biểu sau?

A. Phương pháp tối thiểu hóa bằng biến đại số luôn cho ta kết quả tối thiểu

B. Phương pháp tối thiểu hóa bằng biến đại số không cho ta kết quả tối thiểu

C. Phương pháp tối thiểu hóa bằng biến đại số sẽ không cho ta biết được biểu thức thu được là tối thiểu hay chưa

D. Phương pháp tối thiểu hóa bằng biến đại số cho ta kết quả tối thiểu dựa trên số lượng biến đầu vào

Với đầu vào là AB sau khi qua cổng XNOR thì kết quả thu được:

Cho hàm n biến. Khi đó để biểu diễn hàm bằng phương pháp bảng chân lý ta cần

Với đầu vào là AB sau khi qua cổng XOR thì kết quả thu được:

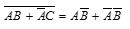

Hãy chỉ ra biểu thức đúng trong các biểu thức sau:

A.

B.

C. A + AB = A

D. Tất cả các biểu thức

Hãy chỉ ra biểu thức đúng trong các biểu thức sau:

Với đầu vào là A = 0 và B = 0 ta thu được:

A. FNAND(AB) = 3

B. FNAND(AB) = 1

C. FNAND(AB) = 2

D. FNAND(AB) = 0

A. Cổng XNOR có thể được tạo thành từ cổng NOR hoặc NAND

B. Cổng XNOR không thể tạo thành từ cổng NAND

C. Tất cả đều sai

D. Cổng XNOR chỉ có thể được tạo thành từ cổng NOR

Giả sử cho 2 biến logic A và B. Hàm F thực hiện phép NAND giữa 2 biến nhận giá trị bằng 0. Khi đó A, B sẽ có giá trị bằng bao nhiêu?

A. A = 1, B = 1

B. A = 1, B=0

C. A = 0, B = 0

D. A = 1, B = 0